MSET30(D1)

EXORset 30

User's Guide

**MICROSYSTEMS**

### CHAPTER 1

### GENERAL INFORMATION

### 1.1 INTRODUCTION

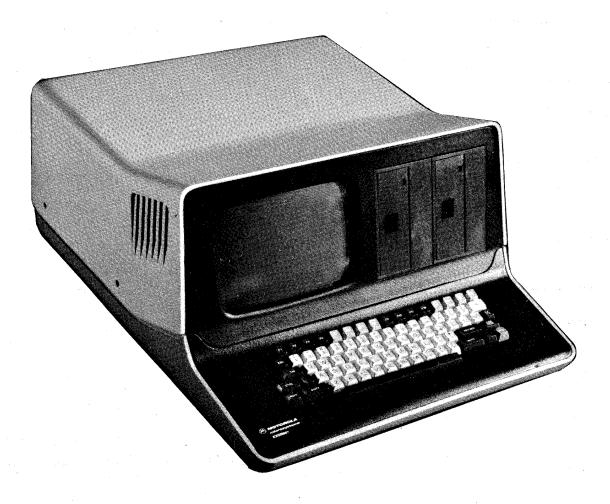

The EXORset is a cost-effective, compact, powerful development tool used in the design and development of microcomputer systems.

The EXORset is made up of seven distinct functional units:

- . The EXORset Main Controller Board.

- The 9" CRT.

- The dual mini-floppy assembly.

The Floppy Disk Controller and 16K-byte RAM board.

- . The ASCII keyboard and function keys assembly.

- . The power supply unit.

- . The enclosure.

Figure 1-1. Typical EXORset System

### 1.2 SPECIFICATIONS

The specifications of the various functional units are identified in the following paragraphs.

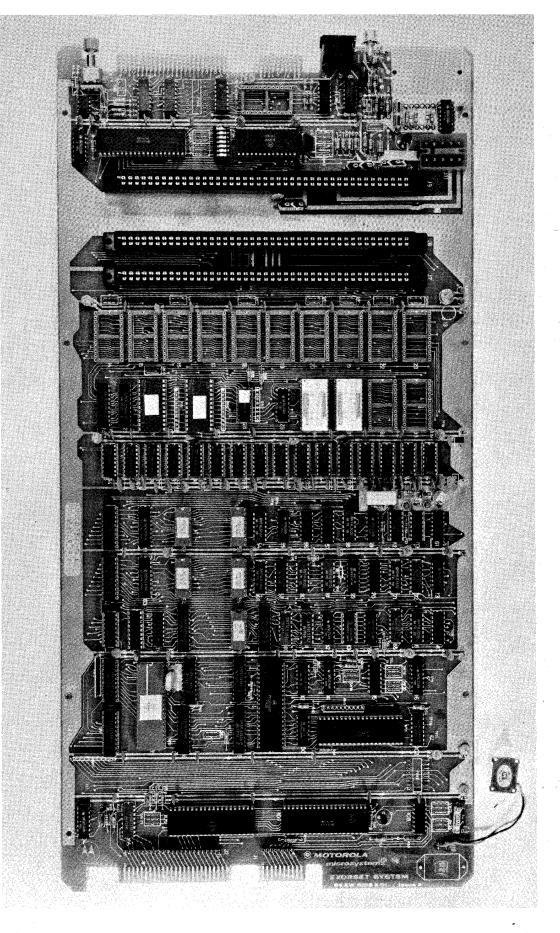

## 1.2.1 Main Controller Board Specifications

Power requirements (max)

5V/6A, +12V/1A, -12V/1A

Operating temperature

0 to 50 deg.C

Processor

MC6809

Word size

Data

8 bits

Address

16 bits

Instructions

8, 16, 24, 32 bits

Instructions

59 instruction mnemonics

Addressing modes

10

Clock cycle time

1 microsecond

Baud rates

110 - 2400

Memory size

up to 32K bytes of RAM and up to 24K bytes

of EROM available to user.

Serial interface

Input

EIA RS-232C

Output

EIA RS-232C

Physical Characteristics

Dimensions (WxD)

Board thickness

.063 in. (1.6 mm)

I/O connectors

Parallel interface

Serial interface

Cassette

50-pin card edge connector

20-pin card edge connector

5-pole DIN connector

CRT

Coax connector

Keyboard

ASCII: flex-tail, 23-pin or card edge, 50-pin

9.76 in. (248 mm) x 19.84 in. (504 mm)

Function keys: flex-tail, 8-pin or card edge,

20-pin

FIGURE 1-2. Main Controller Board

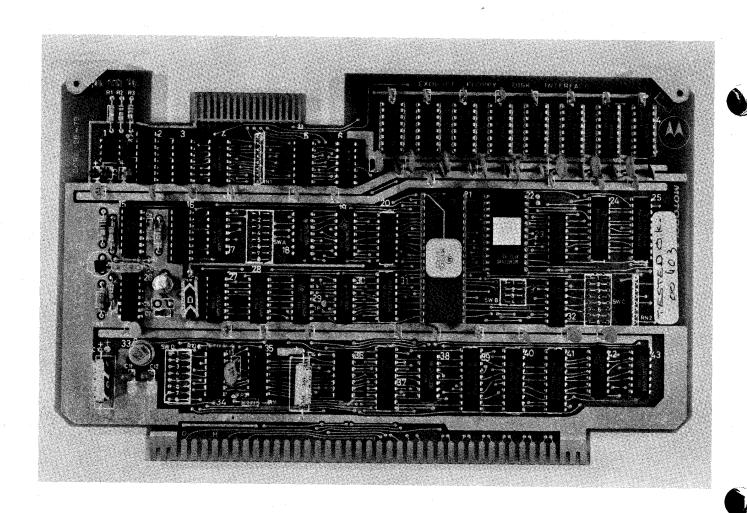

# 1.2.2 Floppy Disk Controller Board Specifications

Power requirements (max)

5V/0.8A, +12V/0.2A, -12V/0.15A

Operating temperature

0 to 50 deg.C

Memory size

16K bytes of RAM, 1K bytes of EROM

(disk driver)

Interface

Output

Input

TTL open collector

220/330 ohm line terminations

Physical characteristics

Dimensions (WxD)

Board thickness

Connector, I/O

Connector, bus

9.76 in. (248 mm) x 5.75 in. (146 mm)

.063 in. (1.6 mm)

34-pin card edge connector

86-pin card edge connector

Figure 1-3. Floppy Disk Controller Board

|     | Т        | ABLE 2-1. EXORset Expansion Bus Signals (J7,J8,J9)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | SIGNAL   | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Α   | +5 Vdc   | +5 Vdc POWER - Used for the system logic circuits and available to the user for prototype module requirements (10 amps tot. max).                                                                                                                                                                                                                                                                                                                                                            |

| В   | +5 Vdc   | +5 Vdc POWER - Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| С   | +5 Vdc   | +5 Vdc POWER - Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D   | IRQnot   | INTERRUPT REQUEST - A low level sensitive input signal to the MPU used to request generation of an MPU interrupt sequence. This signal is latched every cycle during Q high, but will not be received by the MPU until the following bus cycle. At that time, if the interrupt mask bit in the MPU Condition Code Register is not set, the MPU will begin executing the interrupt sequence.                                                                                                  |

| E   | NMInot   | NON-MASKABLE INTERRUPT - A low going edge sensitive input signal to the MPU used to request generation of a MPU non-maskable interrupt sequence. When sampled low one cycle after being sampled high (samples taken every cycle during Q high), an NMI will be triggered. The MPU will recognize the signal on the following bus cycle and begin a non-maskable interrupt sequence at that time, regardless of the logic state of the Interrupt Mask Bit in the MPU Condition Code Register. |

| F   | VMA      | VALID MEMORY ADDRESS - This signal is connected to $+5V$ in the EXORset.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Н   | 44 e4 e4 | NOT USED - Reserved for system expansion.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| J   | E        | E - Clock signal generated by the clock circuitry on the EXORset Main Controller Board. E is similar to phase 2 clock in 6800 systems. Data is placed on the bus during E.                                                                                                                                                                                                                                                                                                                   |

| K   | GND      | GROUND - Power ground for +/- 12 Vdc.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| L   | MEMCLK   | MEMORY CLOCK - Ungated, TTL level clock signal, in phase with E.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| М   | -12Vdc   | -12 Vdc POWER - Used for system logic and available to the user for custom designed prototype modules (1.0 A max).                                                                                                                                                                                                                                                                                                                                                                           |

| N   |          | NOT USED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Р   | ВА       | BUS AVAILABLE - This signal, decoded with Bus Status (BS) indicates the MPU state :                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |          | BA BS 0 0 Normal 0 1 Interrupt Acknowledge 1 0 Sync. Acknowledge 1 1 Halt or Bus Grant                                                                                                                                                                                                                                                                                                                                                                                                       |

MEMORY READY - Not used in the EXORset.

R

MEMRDY

|      | Table   | e 2-1. EXORset Expansion Bus Signals (J7,J8,J9) (cont'd)                                                                                                                                                                                                                                                                                                                          |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN  | SIGNAL  | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |

| S    | LIC     | LAST INSTRUCTION CYCLE - Not used in the EXORset.                                                                                                                                                                                                                                                                                                                                 |

| T    | +12Vdc  | +12 Vdc POWER - Used for the system logic and available to the user for custom designed prototype modules (5.0 A max).                                                                                                                                                                                                                                                            |

| U    | STANDBY | STANDBY POWER - Not used in the EXORset.                                                                                                                                                                                                                                                                                                                                          |

| ٧.   | PWRFAIL | POWER FAIL - Not used in the EXORset                                                                                                                                                                                                                                                                                                                                              |

| W    | PARITY  | PARITY ERROR - Not used in the EXORset.                                                                                                                                                                                                                                                                                                                                           |

| X    | GND     | GROUND                                                                                                                                                                                                                                                                                                                                                                            |

| Y    | GND     | GROUND                                                                                                                                                                                                                                                                                                                                                                            |

| Z    | GND     | GROUND                                                                                                                                                                                                                                                                                                                                                                            |

| Anot | FIRQnot | FAST INTERRUPT - A low level sensitive input to the MPU used to request generation of an MPU fast interrupt sequence. The MPU will wait until it completes the instruction being executed before it recognizes the request. At that time, if the fast interrupt mask bit in the MPU Condition Code Register is not set, the MPU will begin executing the fast interrupt sequence. |

| Bnot | GND     | GROUND                                                                                                                                                                                                                                                                                                                                                                            |

| Cnot | RASnot  | ROW ADDRESS STROBE - This signal, generated by the EXORset Main Controler Board is used to control the 16K RAM block located on the Floppy-Disk Controller Board. This signal is only connected to the first (J07) bus expansion connector.                                                                                                                                       |

| Dnot | CASnot  | COLUMN ADDRESS STROBE - Same as RAS above.                                                                                                                                                                                                                                                                                                                                        |

| Enot | EAHL    | ADDRESS HIGH/LOW - Same as RAS above .                                                                                                                                                                                                                                                                                                                                            |

| Fnot |         | USER DEFINED - This signal may be used for custom modules.                                                                                                                                                                                                                                                                                                                        |

| Hnot | D3not   | DATA (bit 3) - One of 8 bi-directional data lines used to provide a two-way data transfer between the MPU and all other plug-in modules within the system. The data bus drivers on the other modules are in their off or high impedance state except when selected during a memory read or write operation.                                                                       |

| Jnot | D7not   | DATA (bit 7) - Same as D3not on pin Hnot.                                                                                                                                                                                                                                                                                                                                         |

| Knot | D2not   | DATA (bit 2) - Same as D3not on pin Hnot.                                                                                                                                                                                                                                                                                                                                         |

| Lnot | D6not   | DATA (bit 6) - Same as D3not on pin Hnot.                                                                                                                                                                                                                                                                                                                                         |

| Mnot | A14     | ADDRESS (bit $14$ ) - One of the $16$ address lines from the MPU that permits the MPU to select any addressable memory location within the EXORset.                                                                                                                                                                                                                               |

|      | TABLE    | 2-1. EXORset Expansion Bus Signals (J7, J8, J9) (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN  | SIGNAL   | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Nnot | A13      | ADDRESS (bit 13) - Same as A14 above.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pnot | A10      | ADDRESS (bit 10) - Same as A14 above.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Rnot | A9       | ADDRESS (bit 9) - Same as A14 above.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Snot | A6       | ADDRESS (bit 6) - Same as A14 above.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Tnot | A5       | ADDRESS (bit 5) - Same as A14 above.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Unot | A2       | ADDRESS (bit 2) - Same as A14 above.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Vnot | A1       | ADDRESS (bit 1) - Same as A14 above.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Wnot | GND      | GROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Xnot | GND      | GROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ynot | GND      | GROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1    | +5 Vdc   | +5 Vdc POWER - Used for the system logic circuits and available to the user for prototype module requirements (10 A total max).                                                                                                                                                                                                                                                                                                                              |

| 2    | +5 Vdc   | +5 Vdc POWER - Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3    | +5 Vdc   | +5 Vdc POWER - Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4    | G/H      | GO/HALT - When this input to the MPU is in the high state, the MPU will fetch the instruction addressed by the program counter and start instruction execution. When low, all activity in the MPU will be halted. This input is level sensitive.                                                                                                                                                                                                             |

| 5    | RESETnot | RESET - This buffered input signal to the MPU is used to restart the EXORset when power is initially applied. Restart occurs on the low-to-high transition of the RESTART signal. If the RESTART pushbutton switch, located on the Main Controller Board, is depressed while the system is operating, the low-to-high transition of the RESET signal will cause the MPU to execute the EXORbug restart routine or the restart routine indicated by the user. |

| 6    | R/W      | READ/WRITE - This signal is generated by the MPU and indicates to the other modules contained within the system that the MPU is performing a memory read (high) or write (low) operation. The normal standby state of this signal is read (high). Additionally, when the MPU is halted, this signal will be in the read state.                                                                                                                               |

| 7    | Q        | ${\tt Q}$ - A quadrature clock signal generated by the MPU which leads the E (enable) signal. Addresses from the MPU will be guaranteed valid with the leading edge of ${\tt Q}_\bullet$                                                                                                                                                                                                                                                                     |

|     | TABLE       | 2-1. EXORset Expansion Bus Signals (J7,J8,J9) (cont'd)                                                                                                                                                                   |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | SIGNAL      | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                              |

|     | 0.45        | 000000                                                                                                                                                                                                                   |

| 8   | GND         | GROUND - Power ground for +/-12Vdc.                                                                                                                                                                                      |

| 9   | GND         | GROUND - Power ground for +/-12Vdc.                                                                                                                                                                                      |

| 10  | VUA         | VALID USER'S (ALTERNATE MAP) ADDRESS - This signal, when high, allows additional module(s) to respond in address map 2.                                                                                                  |

| 11  | -12Vdc      | -12Vdc POWER - Used for the system logic circuits and available to the user for custom designed prototypes modules (1.0 A max).                                                                                          |

| 12  | REFREQ      | REFRESH REQUEST - Not used in the EXORset. Due to its design concept, the EXORset does not provide the capability of stretching the clock, thus does not allow the use of cycle stealing mode of dynamic memory refresh. |

| 13  | REFGNT      | REFRESH GRANT - Same remark as above.                                                                                                                                                                                    |

| 14  | DEBUG       | DEBUG - Not used in the EXORset.                                                                                                                                                                                         |

| 15  | TSG         | THREE-STATE GRANT - Not used in the EXORset.                                                                                                                                                                             |

| 16  | +12Vdc      | +12Vdc POWER - Used for the system logic circuits and available to the user for prototype module requirements.                                                                                                           |

| 17  | STANDBY     | STANDBY POWER - Not used in the EXORset.                                                                                                                                                                                 |

| 18  | CLOCK       | CLOCK - Not used in the EXORset.                                                                                                                                                                                         |

| 19  | VXA         | VALID EXECUTIVE (ALTERNATE MAP) ADDRESS - This signal, when high, allows additional module(s) to respond in address map 1.                                                                                               |

| 20  | GND         | GROUND                                                                                                                                                                                                                   |

| 21  | GND         | GROUND                                                                                                                                                                                                                   |

| 22  | GND         | GROUND                                                                                                                                                                                                                   |

| 23  | BS          | BUS STATUS - This signal, decoded with Bus Available (BA) indicates the MPU state :                                                                                                                                      |

|     |             | BA BS 0 0 Normal 0 1 Interrupt Acknowledge 1 0 Sync. Acknowledge 1 1 Halt or Bus Grant                                                                                                                                   |

| 24  | GND         | GROUND                                                                                                                                                                                                                   |

| 25  | *** *** *** | USER DEFINED - This signal line may be used for custom modules.                                                                                                                                                          |

| 26  |             | USER DEFINED - Same as above.                                                                                                                                                                                            |

|            |          | Expansion Bu    |           | (17 10 10)            | 7 111        |

|------------|----------|-----------------|-----------|-----------------------|--------------|

| エルロロ に ツ コ | LYDDcat  | Lynancian Ru    | o Cianale | 1.17 .18 .101         | / CONT ' d ) |

| TABLE 2-1. | FAUR SEL | EXUALIST OHE DU | s siunais | 10/200203/            | 1 Cont a)    |

|            |          |                 |           | \ · · · · · · · · · / | \ · · · · /  |

|     | INDEL  | Z-1. Exologic Expansion bus signated (or, so, so) (come a) |

|-----|--------|------------------------------------------------------------|

| PIN | SIGNAL | SIGNAL NAME AND DESCRIPTION                                |

| 27  |        | USER DEFINED - Same as above.                              |

| 28  |        | USER DEFINED - Same as above.                              |

| 29  | D1not  | DATA (bit 1) - Same as D3not on pin Hnot.                  |

| 30  | D5not  | DATA (bit 5) - Same as above.                              |

| 31  | D0not  | DATA (bit 0) - Same as above.                              |

| 32  | D4not  | DATA (bit 4) - Same as above.                              |

| 33  | A15    | ADDRESS (bit 15) - Same as A14 on pin Mnot.                |

| 34  | A12    | ADDRESS (bit 12) - Same as above.                          |

| 35  | A11    | ADDRESS (bit 11) - Same as above.                          |

| 36  | A8     | ADDRESS (bit 8) - Same as above.                           |

| 37  | A7     | ADDRESS (bit 7) - Same as above.                           |

| 38  | A4     | ADDRESS (bit 4) - Same as above.                           |

| 39  | А3     | ADDRESS (bit 3) - Same as above.                           |

| 40  | A0     | ADDRESS (bit 0) - Same as above.                           |

| 41  | GND    | GROUND                                                     |

| 42  | GND    | GROUND                                                     |

| 43  | GND    | GROUND                                                     |

|     |        |                                                            |

TABLE 2-2. Parallel I/O Connector Pin Assignments (J4)

| PIN | SIGNAL | SIGNAL NAME AND DESCRIPTION                                                                                                                                        |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | INPUT  | INPUT PRIME - A low-level output signal which clears the printer buffer and initializes the logic. (Not used by all printers).                                     |

| 3   | GND    | GROUND - Printer interface ground.                                                                                                                                 |

| 5   | FAULT  | FAULT - A low-level input signal that indicates a printer fault condition such as paper empty, light detect, or a desselect condition. (Not used by all printers). |

| 7   | GND    | GROUND - Same as pin 3.                                                                                                                                            |

| TABLE 2-2. | Parallel | I/0 | Connector | Pin | Assignments | (J4) | ) ( | (cont'd) | ) |

|------------|----------|-----|-----------|-----|-------------|------|-----|----------|---|

|------------|----------|-----|-----------|-----|-------------|------|-----|----------|---|

| PIN | SIGNAL     | SIGNAL NAME AND DESCRIPTION                                                                                                 |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------|

| 9   | PB7        | PERIPHERAL DATA LINE (PB7) - Audio-cassette Receive Data.                                                                   |

| 11  | PB6        | PERIPHERAL DATA LINE (PB6) - Audio-cassette Transmit Data.                                                                  |

| 13  | PB5        | PERIPHERAL DATA LINE (PB5) - Free.                                                                                          |

| 15  | PB4        | PERIPHERAL DATA LINE (PB4) - Free.                                                                                          |

| 17, | PB3        | PERIPHERAL DATA LINE (PB3) - Free.                                                                                          |

| 19  | BUSY       | BUSY - An input signal indicationg that the printer cannot receive data.                                                    |

| 21  | OUT-PP     | OUT OF PAPER - A high-level input indicating the printer is out of paper.                                                   |

| 23  | SEL        | SELECT - A high-level input signal indicating that the printer is selected.                                                 |

| 25  | PD8        | PERIPHERAL DATA LINE (PD8) - Output data to printer from PA7 of PIA.                                                        |

| 27  | PD7        | PERIPHERAL DATA LINE (PD7) - Same as pin 25 except bit A6.                                                                  |

| 29  | PD6        | PERIPHERAL DATA LINE (PD6) - Same as pin 25 except bit A5.                                                                  |

| 31  | PD5        | PERIPHERAL DATA LINE (PD5) - Same as pin 25 except bit A4.                                                                  |

| 33  | PD4        | PERIPHERAL DATA LINE (PD4) - Same as pin 25 except bit A3.                                                                  |

| 35  | PD3        | PERIPHERAL DATA LINE (PD3) - Same as pin 25 except bit A2.                                                                  |

| 37  | PD2        | PERIPHERAL DATA LINE (PD2) - Same as pin 25 except bit A1.                                                                  |

| 39  | PD1        | PERIPHERAL DATA LINE (PD1) - Same as pin 25 except bit AO.                                                                  |

| 41  | GND        | GROUND - Same as pin 3.                                                                                                     |

| 43  | DATASTB    | DATA STROBE - A 1.0 microsecond output pulse used to clock data from the MPU to the printer logic.                          |

| 45  | GND        | GROUND - Same as pin 3.                                                                                                     |

| 47  | ACKNLG     | ACKNOWLEDGE - A low-level input pulse indicating the input of a character into memory or the end of a functional operation. |

| 49  | GND        | GROUND - Same as pin 3.                                                                                                     |

| A11 | even numbe | rs (2-50) : GROUND.                                                                                                         |

MATING CONNECTOR : 3M 3415-0001 or equivalent.

TABLE 2-13. EXORset Main Controller Board Jumper Options

|   | JUMPER                |                              |                       | FUNCTION                                                                                   |

|---|-----------------------|------------------------------|-----------------------|--------------------------------------------------------------------------------------------|

|   | SW2-1<br>(OUT)        | SW2-2<br>(OUT)               |                       | PIA1 data lines:  703  PB6 available on J4 pin 11  PB7 available on J4 pin 9               |

|   | IN<br>X               | I N                          | :<br>                 | PB6 available on J4 pin 11 PB7 available on J4 pin 9                                       |

|   | SW3-1<br>(OUT)        | SW3-2<br>(OUT)               | SW3-3<br>(OUT)        | PIA1 B-side interrupt :                                                                    |

|   | IN<br>OUT<br>OUT      | OUT<br>IN<br>OUT             | OUT<br>OUT<br>IN      | to MPU NMI to MPU FIRQ to MPU IRQ                                                          |

| - | SW4-1<br>(IN)         | SW4-2<br>(OUT)               | SW4-3<br>(OUT)        | ACIA interrupt :                                                                           |

|   | IN<br>OUT<br>OUT      | OUT<br>IN<br>OUT             | OUT<br>OUT<br>IN      | to MPU NMI<br>to MPU FIRQ<br>to MPU IRQ                                                    |

| - | SW5-1<br>(OUT)        | SW5-2<br>(OUT)               | SW5-3<br>(OUT)        | Micromodule 11 supply :                                                                    |

|   | IŅ                    | IN                           | IN                    | +5 Vdc, -12 Vdc, +12 Vdc available for Micromodule 11 on J3 pin 16, 18 and 20 respectively |

| - | SW6-1<br>(OUT)        | SW6-2<br>(OUT)               | SW6-3<br>(OUT)        | PIA1 A-side interrupt :                                                                    |

|   | IN<br>OUT<br>OUT      | OUT<br>IN<br>OUT             | OUT<br>OUT<br>IN      | to MPU NMI<br>to MPU FIRQ<br>to MPU IRQ                                                    |

| - | SW7-1<br>(IN)         | SW7-2<br>(OUT <sub>)</sub> ) | SW7-3<br>(OUT)        | PTM interrupt :                                                                            |

|   | IN<br>OUT<br>OUT      | OUT<br>IN<br>OUT             | OUT<br>OUT<br>IN      | to MPU NMI<br>to MPU FIRQ<br>to MPU IRQ                                                    |

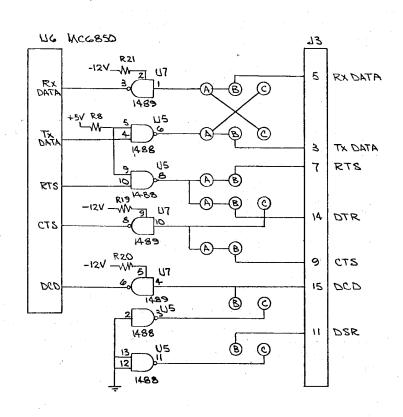

| • | SEE F                 | GURE 2                       | -1.                   | RS-232C interface :                                                                        |

| • | SW9<br>1 to 4<br>(IN) | 1                            | SW9<br>2 to 3<br>(IN) | Graphic RAM base address :                                                                 |

|   | 1-4<br>1-4<br>2-4     | <b>.</b> .                   | 1-3<br>2-3<br>1-3     | 0000<br>4000<br>8000                                                                       |

|   | TABLE 2-1       | 3. EXORset     | Main Controller Board Jumper Options (cont'd)                  |

|---|-----------------|----------------|----------------------------------------------------------------|

|   | JUMPER          |                | FUNCTION                                                       |

|   | SW10-1<br>(OUT) | SW10-2<br>(IN) | 2K/4K EPROM option :                                           |

|   |                 | IN<br>OUT      | 2K EPROM device in socket U14<br>4K EPROM device in socket U14 |

|   | SW11-1<br>(OUT) | SW11-2<br>(IN) | 2K/4K EPROM option :                                           |

|   | OUT<br>I N      | IN<br>OUT      | 2K EPROM device in socket U16<br>4K EPROM device in socket U16 |

|   | SW12-1<br>(OUT) | SW12-2<br>(IN) | 2K/4K EPROM option :                                           |

|   | OUT<br>IN       | IN<br>OUT      | 2K EPROM device in socket U18<br>4K EPROM device in socket U18 |

|   | SW13-1<br>(OUT) | SW13-2<br>(IN) | 2K/4K EPROM option:                                            |

|   | OUT<br>IN       | IN<br>OUT      | 2K EPROM device in socket U20<br>4K EPROM device in socket U20 |

|   | SW14-1<br>(OUT) | SW14-2<br>(IN) | 2K/4K EPROM option :                                           |

|   | OUT<br>IN       | IN<br>OUT      | 2K EPROM device in socket U31<br>4K EPROM device in socket U31 |

|   | SW15-1<br>(OUT) | SW15-2<br>(IN) | 2K/4K EPROM option :                                           |

| • | OUT<br>IN       | IN<br>OUT      | 2K EPROM device in socket U22<br>4K EPROM device in socket U22 |

|   | SW16-1<br>(OUT) | SW16-2<br>(IN) | 2K/4K EPROM option :                                           |

|   | OUT<br>IN       | IN<br>OUT      | 2K EPROM device in socket U33<br>4K EPROM device in socket U33 |

|   | SW17-1<br>(OUT) | SW17-2<br>(IN) | Address decode PROMs select :                                  |

|   | IN<br>OUT       | OUT<br>IN      | PROM chip select to GND PROM only selected during MPU access   |

|     | JUMPER                              |                                     |                               | FUNCTION                                                                                                                          |

|-----|-------------------------------------|-------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|     | SW18-1<br>(OUT)                     | SW18-2<br>(OUT)                     | SW18-3<br>(OUT)               | EXORset initialization at power-up:                                                                                               |

|     | OUT<br>IN<br>X<br>X<br>X<br>X       | X<br>X<br>OUT<br>IN<br>X<br>X       | X<br>X<br>X<br>X<br>OUT<br>IN | 80 characters / line display<br>40 characters / line display<br>50 Hz (EUR)<br>60 Hz (USA)<br>MAP 1<br>MAP 2                      |

|     | SW19-1<br>(OUT)                     | SW19-2<br>(IN)                      | SW19-3<br>(OUT)               | PIA3 A-side interrupt :                                                                                                           |

|     | IN<br>OUT<br>OUT                    | OUT<br>IN<br>OUT                    | OUT<br>OUT<br>IN              | to MPU FIRQ<br>to MPU NMI<br>to MPU IRQ                                                                                           |

|     | SW20-1<br>(OUT)                     | SW20-2<br>(OUT)                     | SW20-3<br>(OUT)               | PIA3 B-side interrupt :                                                                                                           |

|     | IN<br>OUT<br>OUT                    | OUT<br>IN<br>OUT                    | OUT<br>OUT<br>IN              | to MPU FIRQ<br>to MPU NMI<br>to MPU IRQ                                                                                           |

|     | SW21-1<br>(OUT)                     | SW21-2<br>(OUT)                     | SW21-3<br>(OUT)               | Keyboard encoder language selection :                                                                                             |

|     | OUT<br>IN<br>OUT<br>IN<br>OUT<br>IN | OUT<br>IN<br>OUT<br>OUT<br>IN<br>IN | OUT<br>OUT<br>IN<br>IN<br>IN  | English Spanish German Swedish Norwegian / Danish French                                                                          |

|     |                                     |                                     |                               | NOTE: for languages other than english (standard), the character generator and the keyboard key tops must be changed accordingly. |

|     | SW22-1<br>(OUT)                     | SW22-2<br>(OUT)                     | SW22-3<br>(IN)                | PIA2 B-side interrupt :                                                                                                           |

|     | IN<br>OUT<br>OUT                    | OUT<br>IN<br>OUT                    | OUT<br>OUT<br>IN              | to MPU IRQ<br>to MPU FIRQ<br>to MPU NMI                                                                                           |

| *** | SW23-1<br>(OUT)                     | SW23-2<br>(OUT)                     | SW23-3<br>(IN)                | PIA2 A-side interrupt :                                                                                                           |

|     | IN<br>OUT<br>OUT                    | OUT<br>IN<br>OUT                    | OUT<br>OUT<br>IN              | to MPU IRQ<br>to MPU FIRQ<br>to MPU NMI                                                                                           |

TABLE 2-13. EXORset Main Controller Board Jumper Options (cont'd)

| <br>JUMPER          |                 |                 | FUNCTION                                                                                                           |

|---------------------|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------|

| <br>SW24-1<br>(OUT) | SW24-2<br>(IN)  |                 | Audio-cassette playback signal phase selection:                                                                    |

| IN<br>OUT           | OUT<br>IN       |                 | playback signal not inverted playback signal inverted                                                              |

|                     |                 |                 | NOTE: some cassette recorders invert the recorded signal, therefore jumper SW24 allows for proper phase recovering |

| <br>SW25-1<br>(OUT) | SW25-2<br>(OUT) | SW25-3<br>(OUT) | Non-standard bus signals :                                                                                         |

| OUT<br>IN           | OUT<br>IN       | OUT<br>IN       | RAS', CAS', EAHL' to J07 only RAS', CAS', EAHL' to J07, J08, J09                                                   |

EXORset as a terminal to a host (EXORciser):

As delivered - printed wire between point A & point B .

EXORset as a modem to a terminal:

Cut printed wire between point A & point B .

Add jumper from point B to point C .

FIGURE 2-1. RS-232C Interface Jumper Options

TABLE 2-14. EXORset Mini-Floppy Disk Controller Board Jumper Options

| SWA-1<br>(OUT)     |                        |                        |                        | Low current signal :                                                               |

|--------------------|------------------------|------------------------|------------------------|------------------------------------------------------------------------------------|

| IN<br>OUT          |                        |                        |                        | to P2 pin 34 (provision for norm. drives) if mini-floppy drives are used           |

| SWA-2<br>(OUT)     |                        |                        |                        | Optional drive 3 :                                                                 |

| IN<br>OUT          |                        |                        |                        | SELECT3 signal to P2 pin 4 not connected                                           |

| <br>SWA-5<br>(OUT) | SWA-6                  |                        |                        | FDC clock select :                                                                 |

| IN<br>OUT          | OUT<br>IN              |                        |                        | 1 MHz clock to FDC (provision for normal drive) 500 KHz clock to FDC (mini-floppy) |

| <br>SWA-7<br>(OUT) | SWA-8                  | 3                      |                        | MEMCLK / E select :                                                                |

| <br>IN<br>OUT      | OUT<br>IN              |                        |                        | MEMCLK signal to FDC / clock divider<br>E signal to clock divider                  |

|                    |                        |                        |                        | 16K RAM base address select :                                                      |

| SWB-4<br>(OUT)     |                        | SWB-2                  |                        |                                                                                    |

| IN O               | OUT<br>OUT<br>IN<br>IN | IN<br>OUT<br>IN<br>OUT | OUT<br>IN<br>OUT<br>IN | 0000<br>4000<br>8000<br>C000                                                       |

TABLE 2-14. EXORset Mini-Floppy Disk Controller Board Jumper Options (cont'd)

| <br>                                              |                                                     |                                                               |                                                                    |                                                                |                                                             |                                                                |                                                                |                                                                                                                      |        |         |

|---------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------|---------|

| FDC a                                             | nd dis                                              | k driv                                                        | er bas                                                             | e addr                                                         | ess:                                                        |                                                                |                                                                |                                                                                                                      |        |         |

| SWC-8<br>(OUT)                                    |                                                     | SWC-6<br>(OUT)                                                |                                                                    | SWC-4<br>(OUT)                                                 | SWC-3                                                       | SWC-2<br>(IN)                                                  | SWC-1<br>(OUT)                                                 |                                                                                                                      |        |         |

| IN IN IN IN IN IN OUT OUT OUT OUT OUT OUT OUT OUT | OUT OUT OUT OUT OUT OUT OUT IN IN IN IN IN IN IN IN | IN IN IN OUT OUT OUT IN IN IN OUT OUT OUT OUT OUT OUT OUT OUT | OUT OUT OUT IN IN IN OUT OUT OUT OUT IN | IN OUT OUT IN OUT OUT IN OUT OUT IN OUT IN OUT OUT OUT OUT OUT | OUT OUT IN OUT IN OUT IN OUT OUT IN IN OUT IN IN OUT OUT IN | IN OUT | OUT IN | 0000<br>1000<br>2000<br>3000<br>4000<br>5000<br>6000<br>7000<br>8000<br>9000<br>A000<br>B000<br>C000<br>D000<br>F000 |        |         |

| SWD-1<br>(OUT)<br>IN                              | SWD-2<br>(IN)<br>OUT                                | 2                                                             | RI<br>RI                                                           | EADY s                                                         | elect<br>generat<br>ignal)                                  | ted o                                                          | n-board<br>he drive                                            | (for                                                                                                                 | drives | without |

| <br>                                              |                                                     |                                                               | M                                                                  | ap ass                                                         | ignment                                                     | t :                                                            |                                                                |                                                                                                                      |        |         |

|                                                   |                                                     | SWD-7<br>(OUT)                                                |                                                                    |                                                                |                                                             |                                                                |                                                                |                                                                                                                      |        | •       |

| IN                                                | OUT                                                 | IN                                                            | OUT                                                                |                                                                | FDC a                                                       | and dis                                                        | sk drive                                                       | · in m                                                                                                               | ap 1   |         |

| IN                                                | OUT                                                 | OUT                                                           | IN                                                                 |                                                                | FDC a                                                       |                                                                | sk drive                                                       | rinm                                                                                                                 | ap 2   |         |

| OUT                                               | IN                                                  | IN                                                            | OUT                                                                | •                                                              | FDC a                                                       |                                                                | sk drive                                                       | rinm                                                                                                                 | ap 2   |         |

| OUT                                               | IN .                                                | OUT                                                           | IN                                                                 |                                                                | FDC a                                                       | RAM in<br>and dis                                              | sk drive                                                       | rinm                                                                                                                 | ap 1   |         |

| OUT                                               | OUT                                                 | X                                                             | <b>X</b> .                                                         | 16K RAM in<br>FDC and di                                       |                                                             |                                                                | sk drive                                                       | r resp                                                                                                               | ond    |         |

| X                                                 | X                                                   | OUT                                                           | OUT                                                                |                                                                | 16K F<br>(dependent)<br>and S<br>FDC a<br>or 2<br>SWD-4     | und disk driver in map 1<br>(depending on SWD-3 and            |                                                                |                                                                                                                      |        |         |

### 1)

### 2.6 USE AS A TERMINAL

The user has the option of connecting the EXORset to a RS-232C compatible device (e.g. an EXORciser). The switch SW4-1 must be installed (selecting NMI) for the EXORbug commands to work. To connect the EXORset to a 20 mA current loop device, use the Micromodule M68MM11 (RS-232C to TTY adapter). Refer to the M68MM11 manual for installation.

For a description of the signals available on the RS-232C connector, refer to Table 2-3.

The necessary cable is a 25-conductor flat cable with a 3M-3461-0001, 2 x 10-pin card edge connector (or equivalent) at the EXORset end (conductors 21 to 25 not used) and ANSLEY 501-659-2, 25-pin connector (or equivalent) at the peripheral end.

To switch the EXORset from the stand-alone mode of operation (off-line) to the terminal mode of operation (on-line), enter the command:

XCOM C/R

To switch the EXORset from the terminal mode of operation (on-line) to the stand-alone mode of operation (off-line), enter the sequence :

ESC-0

Note that this command works only if it is echoed from the host computer.

This serial port is also used by the DWLD and DUMP commands to transfer the contents of memory from, and to, the Host. See paragraph 5.2.10 for other details.

### 2.7 TESTING HARDWARE/SOFTWARE INTERFACES

The EXORset is limited to three module slots so it is not possible to emulate a system in the same way as with an EXORciser, but it is possible to evaluate I/O routines for fairly complex systems. Two module slots are always available and, in special cases, a third one can be used (by using cassette instead of the minifloppies). For example, one or a combination of the following modules can be used:

| MEX6820  | I/O module                     |

|----------|--------------------------------|

| ME X6850 | ACIA module                    |

| M68MM07  | Quad ACIA/SSDA micromodule     |

| M68MM12  | IEEE micromodule               |

| M68MM13  | Digital interface micromodules |

| M68MM05  | A/D, D/A micromodules          |

| M68MM15  | A/D. D/A micromodules          |

The list is not limited to this, and it is also to be noted that EXORset has a FTM, ACIA, and PIA and numerous EROM sockets which can be used to emulate ficomodule 19 and/or Micromodule 4. The modules with VUA enabling will respond ap 2 and, if they can select VXA, they will be in map 1.

As can be seen in Figure 5-3, the standard EXORset (with standard address decoding) has space at EC10 to EF00 for these added I/O devices. Table 5-4 gives the addresses of the built-in PTM, ACIA, and PIA which can be used to emulate Micromodule 19, for example. Tables 5-1, 5-2, and 5-3 give the addresses of various EROM sockets. Paragraph 2.8 explains how these address PROM's can be changed if more exacat emulation is required.

Another factor is whether or not the routines and hardware use interrupts. The I/O modules have provision to connect IRQ; bit if FIRQ or NMI were to be required, it will be necessary to install a jumper on the module.

### NOTE

The user is cautioned to be careful about trying to solder to the gold-plated fingers of the connector, since the solder may run all over the contact unless properly done. The board should be oriented with the connector up and only a very little solder used.

When using interrupts for I/0, it will be necessary to set up a user vector table with second level interrupts, and to change the ATOP vector as described in paragraph 4.4.

When emulating certain system configurations, it may be necessary to change the interrupt connections for EXORset ACIA or PIA1. These are determined by jumpers on SW3, SW4, and SW6. SW4-1 is normally jumpered to NMI to allow the EXORbug commands of XCOM, DWLD, and DUMP to work properly. It is recommended that this jumper be cut and a DIP switch be installed in these locations to allow NMI, IRQ, or FIRQ to be switchable. IRQ or FIRQ would be used in a typical system.

### 2.8 USER-DEFINED ADDRESS MAP

The various memory blocks and I/O devices are decoded using fusible-link PROM's. By reprogramming these PROM's, any configuration of RAM, E/ROM, I/O devices can be redefined, in 256-byte increments. The maximum available address space is 56K bytes in each map. The upper 8K address range is reserved for the system. Tables 5-1, 5-2, and 5-3 in Chapter 5 show the address decode PROM contents corresponding to the EXORset standard memory map. An example is given in paragraph 5-2-4 describing how to define a new address map.

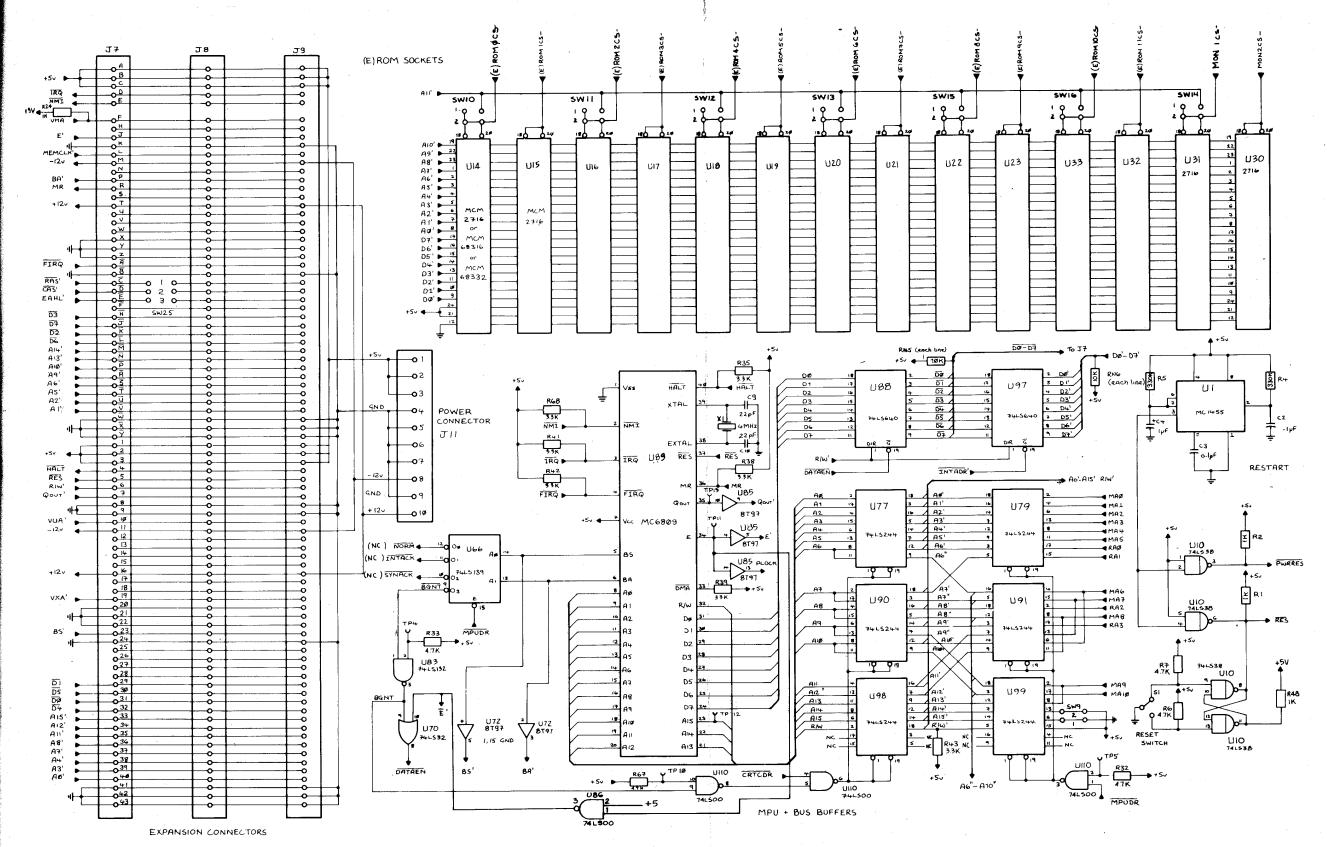

FIGURE 7-1. Main Controller Board Schematic Diagram (Sheet 1 of 3)

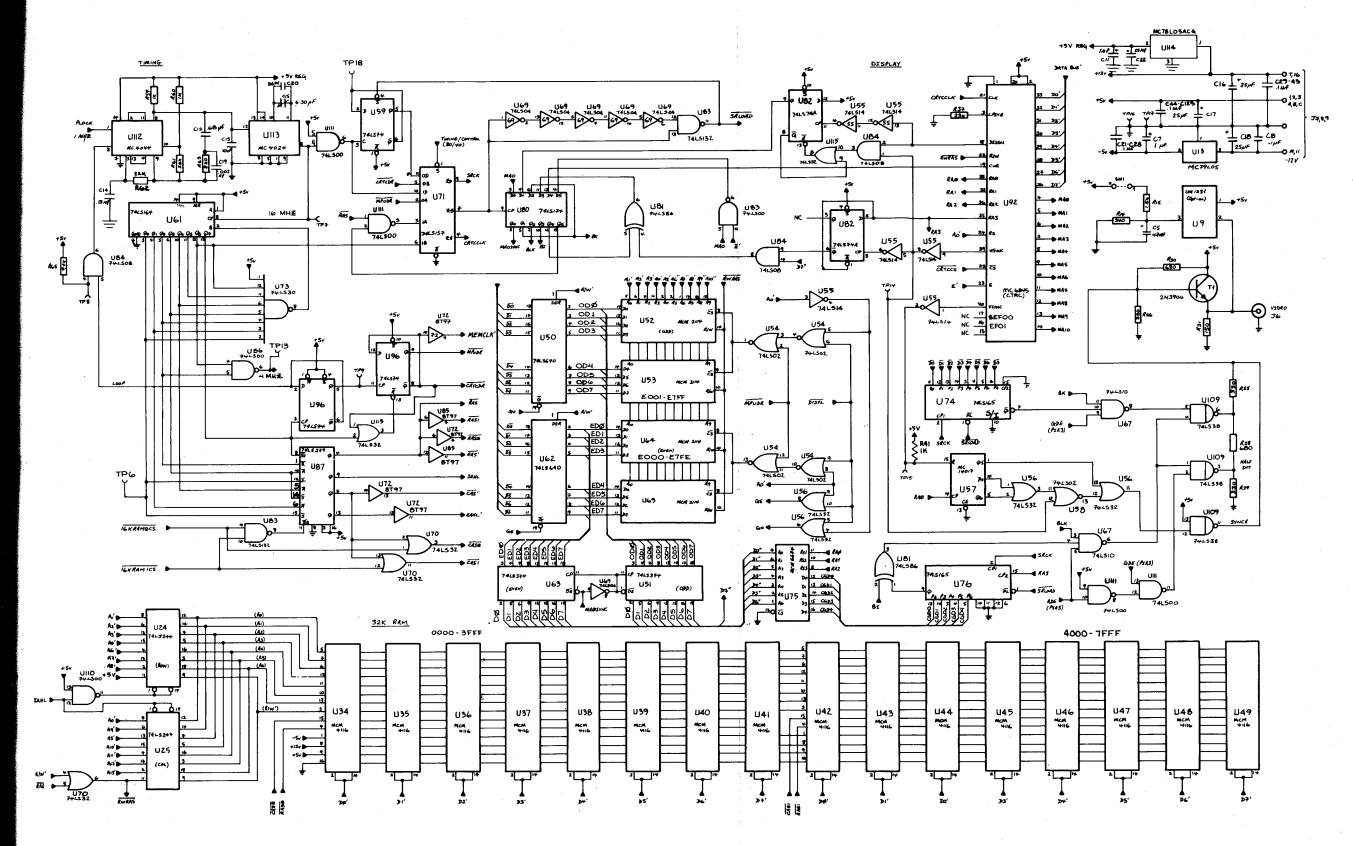

FIGURE 7-1. Main Controller Board Schematic Diagram (Sheet 2 of 3)

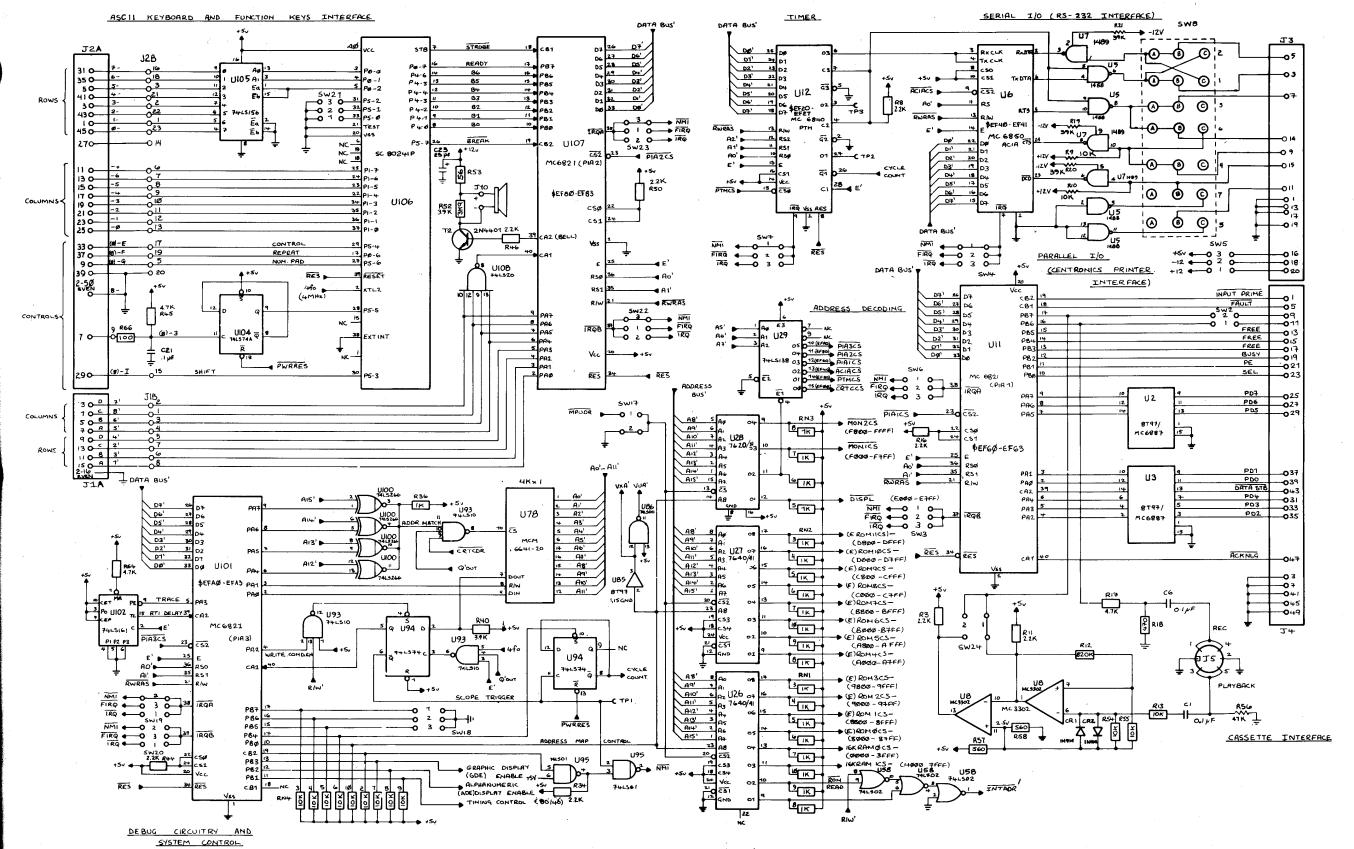

FIGURE 7-1. Main Controller Board Schematic Diagram (Sheet 3 of 3)

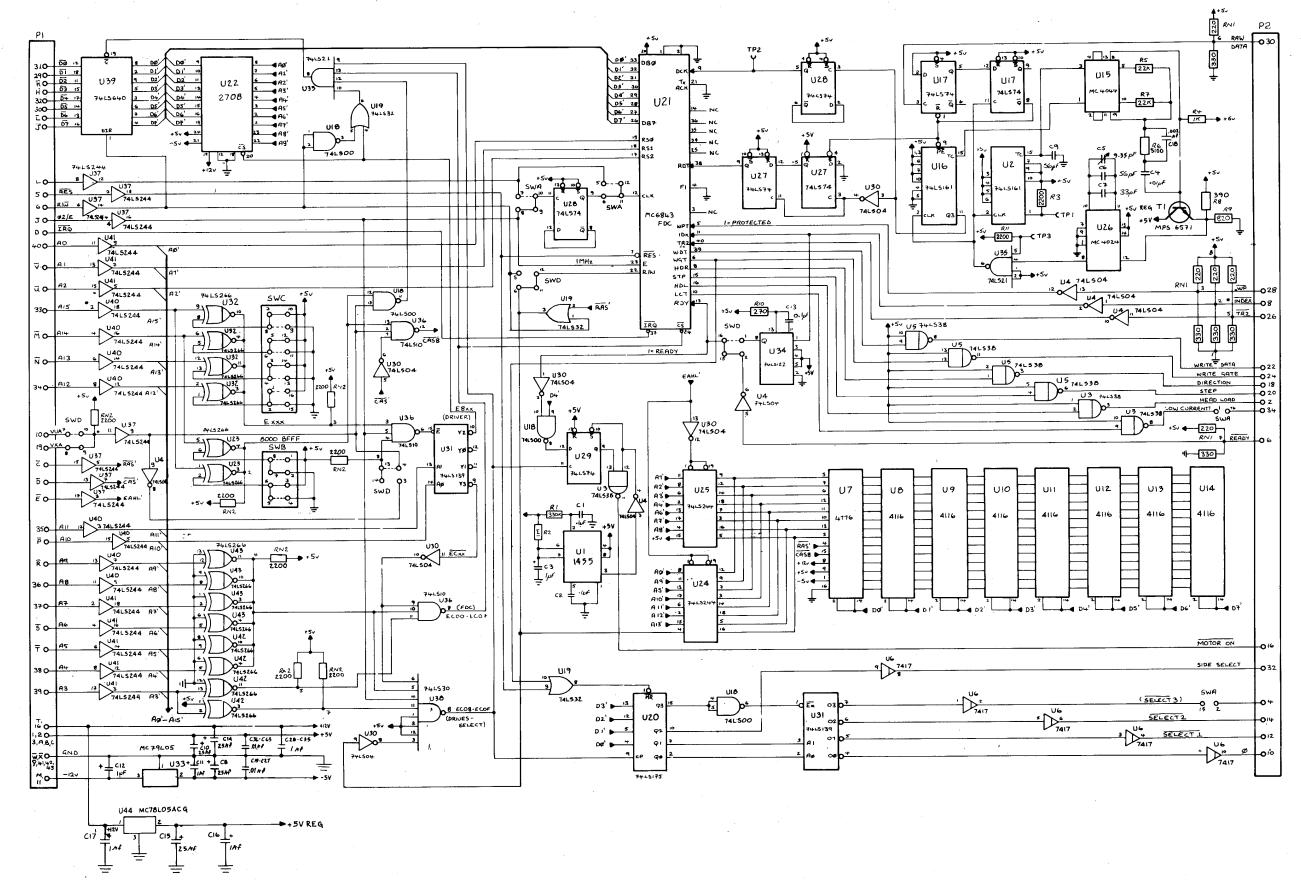

FIGURE 7-2. Floppy Disc Controller Board Schematic